ニュース

DACは、市場全体でAIとMLの役割を探る

サンフランシスコのMoscone Centerが6月25-28日にDACをホストする

OneSpinソリューション そして Austemper Design Systems 両方とも機能的安全性検証のためのツールを強調する。 Austemperは、KaleidoScopeツールスイートを使用してミッションクリティカルなシステム開発に専念し、コンカレントミックスシグナルフォールトプロパゲーションのアナログ設計をサポートします。自動化されたツールスイートは、認証指向アプリケーションのための安全解析、合成、および検証機能を備えています。 ADASおよび自律走行での大規模な自動車設計に使用されます。同時故障シミュレーションには、ASILの要件を満たすためにISO 26262で推奨されているシミュレーションが含まれています。

同社は、OneSpin Solutionsと提携して、OneSpinブースで実演される設計と検証フローを組み合わせて、機能安全アプリケーションにツールサポートの方法論を採用するようにしました。ハードウェアの安全機構はチップ設計に組み込まれ、OneSpin Solutionsのツールはハードウェアの安全ロジックを正式に検証します。等価性検査により、挿入された安全ロジックが通常の機能に影響を与えないことが保証され、障害検出解析により、ランダムなエラーが発生した場合に安全メカニズムが適切に実行されることが検証されます。

OneSpinはまた、TÜVSÜDのツール開発プロセスの検証に続いて、ツール資格認定キットを宣伝しています。イニシャルキットは、FPGA設計フローによるインプリメンテーションエラーの発生を防止する自動シーケンシャル同値チェックである、同社の360 EC-FPGA EDAツールで利用可能です。このキットは、ISO 26262、IEC 61508およびEN 50128の認定を受けています。

FPGAの洞察

FPGAの設計でも、 プルニファイア ザイリンクスと協力して、Plunify Cloudプラットフォームを介してクラウドにVivadoデザインスイートを提供しています。設計者は、Amazon Web Services(AWS)クラウド上でライセンスを含むVivadoプロジェクトをコンパイルするためにわずか50cを支払うだけです。

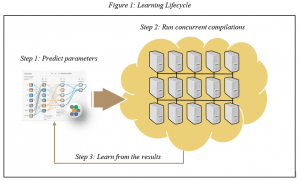

同社はまた、InTimeタイミングクロージャソフトウェアの強化を実証し、クラウドのFPGAタイミングを最適化します(図1)。 InTime Optimization Methodologyは、クロック周波数を20〜80%向上させ、機械学習による数週間ではなく数日のタイミング要件を満たすことができます。また、タイミングクロージャと最適化を高速化し、クラウド経由でアクセスします。

同社はまた、InTimeタイミングクロージャソフトウェアの強化を実証し、クラウドのFPGAタイミングを最適化します(図1)。 InTime Optimization Methodologyは、クロック周波数を20〜80%向上させ、機械学習による数週間ではなく数日のタイミング要件を満たすことができます。また、タイミングクロージャと最適化を高速化し、クラウド経由でアクセスします。

eFPGA技術の推進、 Achronix Semiconductor IPスペシャリストと協力しています キャスト スループットを向上させ、メモリストレージを節約します。

2つの出展者は、CASTのロスレス圧縮IPがAchronix FPGAポートフォリオにどのように移植され、データセンターおよびモバイルエッジデータ転送アプリケーションで使用されるかを説明します。 Deflate、GZIP、ZLIBの可逆圧縮規格のハードウェア実装は、低圧縮と低レイテンシで最大100Gbit / sのスループットを提供する圧縮または復元に使用されるソフトウェア実装と互換性があり、Speedcore eFPGAテクノロジと連携して大きな移動低消費電力のデータ

CASTはIPをAchronixのFPGAに移植しました

エネルギー効率

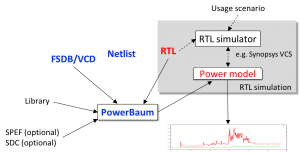

電力管理について言えば、別の出展者、 バウムエネルギー効率がチップ設計における最も未開発の領域であることを示しています。自動化された電力解析およびモデリングツールは、自動車、IoT、モバイル、ネットワーキングおよびサーバープロジェクト向けに設計されています。 PowerBaum 2.0(図3)は、RTLおよびネットリストの記述を取り入れ、動的および静的電力をサポートし、ハードウェアエミュレーションによる電力解析のサポートを追加します。これは、エンジニアが現実的なソフトウェアシナリオでパワーバグを修正することを可能にします。このツールはまた、デザイナーが指定する任意の温度での解析をサポートし、設計の消費電力に対する温度の影響を評価します。

DACでは、PowerBuumと統合して電力モデリング用のゲートレベルの電力解析エンジンであるPowerWurzelも導入する予定です。

図3 Baumのツールはエネルギー効率を分析します

IC設計のためのクラウドベースのSoC設計および検証ツール メトリック シミュレーション要件とリソースを管理し、1分ごとに上下に調整するように設計されたCloud SimulatorとVerification Managerが含まれています。同社は、Google Cloudが無制限のUVM準拠のSystemVerilogシミュレーション能力とネイティブでウェブベースの検証管理を可能にし、回帰時間を短縮し、トランクコードエラーと予測可能なコードカバレッジを削減できると主張しています。

出展者以外にも、このイベントでは、テクニカルセッションと、主題分野に取り組む基調講演プログラムが開催されます。今年は、例えば、ケイデンスは「自動車アプリケーションの機能安全と信頼性」のチュートリアルを、機械学習(「機械学習は次のレベルへの音声認識パフォーマンスを引き出す」)に関するチュートリアルを開催します。 6月25日月曜日、InstrumentalのAnna-Katrina Shedletsky氏による基調講演では、「自動化インテリジェンス:機械学習と製造の未来」に焦点を当てます。南アフリカ大学のMajaMatarić氏による基調講演では、社会的支援ロボット(SAR)にMLとAIを使用して、「自動化vs Augmentation:社会的支援ロボットと作業の将来」を発表します。

もう1つの基調講演では、独自仕様の命令セットアーキテクチャ(ISA)からアーキテクトを解放する手段として、RISC-Vが推奨されています。 David A Patterson、Google、California大学は、「コンピュータアーキテクチャの新しい黄金時代:ドメイン固有のアクセラレータとオープンRISC-V」を発表します。

DACの今年の新しい領域は、Design Infrastructure Alleyです。のイニシアチブ ESDアライアンス および関連 高性能コンピューティングのプロフェッショナル向け 電子システムおよびコンポーネントの設計のためのITインフラストラクチャ専用領域です。クラウドの設計と管理のためのコンピューティングとストレージの要件だけでなく、ライセンス管理、グリッドコンピューティング、データセキュリティについて議論している専用のDesign-on-the-Cloudパビリオンシアターもあります。